|

|

||

|

|||||||||||||||||||

A PIC mikrovezérlök családjában nagy népszerüségnek örvend a 16F84-es típus, köszönhetöen sokoldalúságának. Az iskolánkban müködö mikrokontroller programozó szakkör is a legtöbbet ezzel az IC-vel dolgozik Ez a leírás mindazoknak szeretne segíteni, akik most kezdik az ismerkedést ezen processzorokkal, illetve magyar nyelven könnyebben boldogulnak a dokumentáció olvasásával.

35 db egyszerü utasítás

Minden utasítás-az elágaztatókat

kivéve (2 ciklus)-egy ciklus

Órajel: 0-10MHz

|

Program Memória (szó) |

Adat RAM (bájt) |

Adat EEPROM (bájt) |

|

1k |

|

|

14 bites utasítások

8 bites adatok

8 szintü hardver verem

Közvetlen , közvetett és relatív

címzési módok

4 megszakítási forrás:

-Külsö RB0/INT láb

-TMR0 idözítö túlcsordulás

-PORTB(7-4) változása miatt

-Adat EEPROM írása kész

1000 írási/törlési ciklus (program memória)

10000 írási/törlési ciklus (belsö EEPROM)

Az EEPROM több mint 40 évig megörzi az adatot

13 I/O kivezetés (mindegyik lehet

bemenet vagy kimenet)

Nagyáramú kimenet

TMR0: 8 bites idözítö/számláló

8 bites elöosztóval

Két lábon keresztül történö

soros programozás (ICSP)

Bekapcsolási reset' (POR)

Power-up Timer' (PWRT),

(akkor kapcsolja az órajelet a CPU-ra,

ha az már stabil)

Watchdog Timer (WDT)

(Kiváltja a reset folyamatot, ha nem

normál müködés van)

Program védelem

Minimális fogyasztású (SLEEP) üzemmód

Sokoldalú belsö oszcillátor

Alacsony fogyasztás és nagy sebesség

Széles tápfeszültség tartomány (2-6V)

Alacsony fogyasztás

<2mA (5V, 4MHz)

mA (2V)

< 1mA alvó mód (2V)

A 16F84 Harvard architektúrájú RISC mikroprocesszor. Az ilyen architektúránál külön válik a program és az adat memória (a Neumanni architektúrában ugyanaz a memória szolgál mindkét célra).

A program és az adat memória szétválasztása lehetövé teszi, hogy az utasítás hossza eltérjen a 8 bites adathossztól. A 16F84-ben az utasítás hossza 14 bit, így egyszavas" utasítások is elegendöek. A kétállapotú pipline (csövezeték, sor) segítségével az utasítás lehívás és végrehajtás egymásba lapolódik, következésképpen minden utasítás egy ciklust igényel (kivételt képeznek az elágaztató utasítások).

A 16F84 1kszó (1szó=14bit belsö memóriát kezel.

A 16F84 egy 8bites ALU-t és egy munkargisztert-W:work-(ez tulajdonképpen az akkumulátor) tartalmaz.

Ez az ALU általános célú aritmetikai és logikai egység, amely az adatok valamint a W regiszter, illetve bármelyik fájlregiszter között végzi a müveleteket. Az ALU tud összeadni, kivonni, léptetni, és logikai müveleteket végezni. Az aritmetikai müveleteket kettes komplemensben végzi. Az egyik operandus a W-ben van, a másik valamelyik fájlregiszter vagy konstans(literál). Az eredmény kerülhet a W-be vagy a fájlregiszterbe. A müveletek eredményétöl függöen az ALU a következö jelzöbiteket állítja: C-Carry (átvitel), Z-Zero (zéró), D-Digit Carry (alsó négy biten túlcsordulás). Ezek a jelzöbitek a STATUS regiszterben találhatók. Kivonáskor a C és DC áthozat negált"-ként viselkedik (/borrow, /digit borrow).

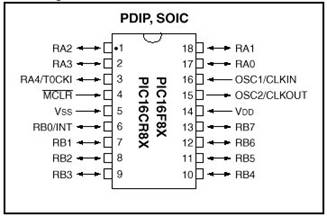

Mint az egyszerüsített blokkvázlatból (1.ábra) látható az

architektúrát úgy alakították ki, hogy az utasítás végrehajtására legyen

optimalizálva.

1.ábra

|

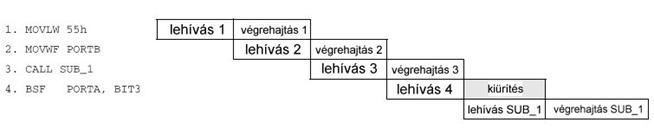

Kivezetés |

Sorszám |

I/O/P típus |

Buffer típus |

Leírás |

|

OSC1/CLKIN |

|

I |

ST/CMOS |

Oszcillátor kristály bemenet/küsö órajel bemenet |

|

OSC2/CLKOUT |

|

O |

|

Oszcillátor kristály kimenet. Ide csatlakozik a kvarc v. a rezonátor kristály oszcillátor módban. RC módban az fosc/4 jel vehetö itt le. |

|

|

|

I/P |

ST |

Általános törlés (reset)-aktív nullás. |

|

RA0 RA1 RA2 RA3 RA4/T0CKI |

|

I/O I/O I/O I/O I/O |

TTL TTL TTL TTL ST |

PORTA: kétirányú I/O port Port vagy TMR0 idözítö/számláló órajel bemenet (nyitott kollektoros |

|

RB0/INT RB1 RB2 RB3 RB4 RB5 RB6 RB7 |

|

I/O I/O I/O I/O I/O I/O I/O I/O |

TTL/ST1 TTL TTL TTL TTL TTL TTL/ST2 TTL/ST2 |

PORTB: kétirányú I/O port, programból bekapcsolható bemeneti felhúzóellenállásokkal Port vagy külsö megszakítás bemenet Megszakítást okoz változás esetén Megszakítást okoz változás esetén Megszakítást okoz változás esetén3 Megszakítást okoz változás esetén4 |

|

Vss |

|

P |

|

Pozitív tápfeszültég |

|

Vdd |

|

P |

|

Földpont |

Jelölések: I=bemenet O=kimenet P=tápfesültség ST=Schmitt-trigger

Megjegyzések:

1: ha külsö megszakítás bemenetnek programozzuk, akkor Schmitt-trigger-es lesz

2: soros programozás (égetés) esetén Schmitt-triggeres

3: programozáskor (égetés) ez az órajelbemenet

4: programozáskor (égetés) ez az adatbemenet

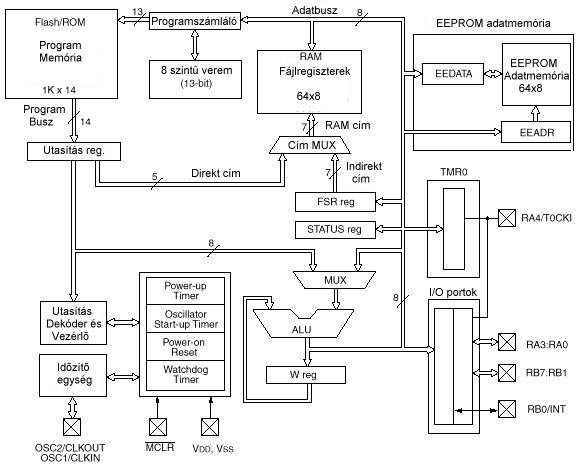

Az oszcillátorban kialakuló négyszögjelet a processzor idözítö egysége néggyel leosztva, négy-egymást át nem lapoló-(Q1,Q2,Q3,Q4) belö órajellé alakítja át. Ez a négy leosztott óraimpulzus alkot egy gépi ciklust. Az utasítás végrehajtása a következöképpen történik (2.ábra):

Q1: a PC értéke eggyel növekszik

Q2-Q4: utasítás lehívás- a CPU kiolvassa a memóriából az utasítást, és az utasításregiszterbe helyezi

Q1-Q4: ezen fázisok alatt történik meg az utasítás dekódolása és végrehajtása, valamint a következö utasítás lehívása

2.ábra

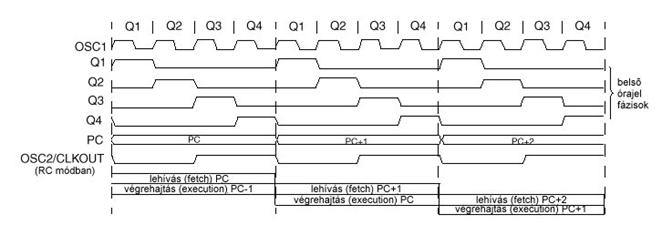

Az utasítások végrehajtásának gyorsítása érdekében a

mikrovezérlö felhasználja a pipeline (csövezeték, sor) elvet

(3.ábra): az éppen aktuális utasítás végrehajtásával párhuzamosan beolvassa a

soron következö utasítást. Ilyen módon egy utasítás végrehajtása egy gépi

ciklust igényel. Kivételt képeznek ez alól az elágaztató utasítások (pl. CALL).

Ezekben az esetekben a sor tartalmát el kell dobni (kiürítés), s az új

utasítást kell lehívni.

3.ábra

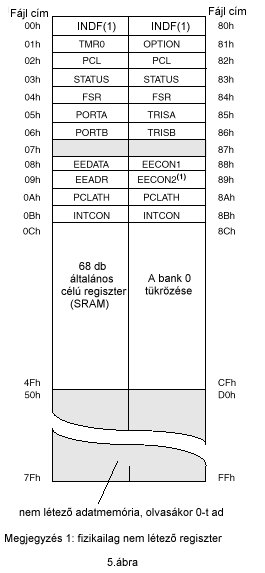

A 16F84 két memória blokkot tartalmaz: program memória és adat memória. Mindkét blokk saját busszal rendelkezik, így bármelyik elérhetö ugyanazon órajelperiódusban. Az adatmemória további két részre bomlik. Az egyik részt az általános célú regiszterek alkotják (general purpose RAM), a másikat pedig a speciális funkciójú regiszterek (SFR- Special Function Register). Ezek a speciális regiszterek állítják be gyakorlatilag a CPU mag és a perifériák müködési módját. Az adat memória területén található a belsö EEPROM is. Az EEPROM memória csak indirekt módon az EEADR (cím) és EEDATA (adat) regiszterek segítségével érhetö el. Az EEPROM memória 64 bájtot tartalmaz, amely írható és olvasható is.

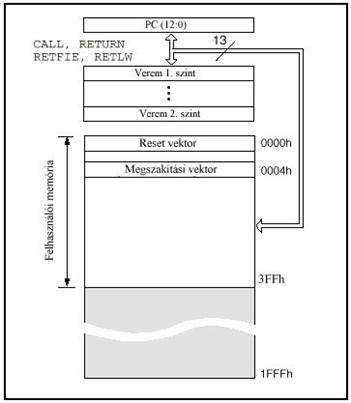

A 16F84 programszámlálója 13 bites, tehát a megcímezhetö memória terület 1kszó (1szó=14 bit).

A címtartomány 0000 h-tól 03FF h-ig terjed. A fizikailag létezö címtartomány feletti címek esetén az elérhetöség a következöképpen alakul: pl. a 20h, 420h, 820h helyeken ugyanaz az utasítás látszik.

A reset vektor a

0000h, a megszakítási vektor pedig a 0004h címen helyezkedik el (4.ábra).

A reset vektor a

0000h, a megszakítási vektor pedig a 0004h címen helyezkedik el (4.ábra).

Az adat memória két partícióra oszlik, úgymint speciális funkciójú regiszterek (SFR), és általános célú regiszterek (GPR). A két partíció két bankra tagolódik. Mindkét bankban van speciális és általános célú regiszter is. A két bank között a STATUS regiszter RP1 és RP0 bitjével tudunk váltani. Mindegyik regiszter elérhetö direkt és indirekt módon is. Az indirekt elérés az FSR (File Select Register) segítségével valósul meg. Mindkét bank 128 bájtot tartalmaz, ebböl az elsö tizenkettö az SFR terület számára van lefoglalva, ezután következik a 68 darab általános célú regiszter (GPR), a fennmaradó terület nem használatos, olvasáskor 0-át ad. A bank 1-ben a bank 0-ban található általános célú regiszterek árnyéka (tükörképe) jelenik meg,

így ugyanazon regiszter mindkét bankból elérhetö. Az SFR-ek között is van olyan, amely mindkét bankból elérhetö (pl. a STATUS regiszter, hiszen e nélkül nem tudnánk bankot váltani.).

Az SFR regiszterek a CPU és a periféria funkciók beállítására szolgálnak.

|

Cím |

Név |

7. bit |

6.bit |

5. bit |

4. bit |

3. bit |

2. bit |

1. bit |

0. bit |

Érték bekap-csolási reset után |

Érték egyéb reset esetén(3) |

|

|

Bank 0 |

||||||||||||

|

00h |

INDF |

Az FSR által kijelölt fájlregiszter adatát tartalmazza (fizikailag nem létezik) |

|

|

||||||||

|

01h |

TMR0 |

8 bites valós idejü számláló/idözítö |

xxxx xxxx |

uuuu uuuu |

||||||||

|

02h |

PCL |

A programszámláló (PC) alsó 8 bitje |

|

|

||||||||

|

03h |

STATUS(2) |

IRP |

RP1 |

RP0 |

|

|

Z |

DC |

C |

0001 1xxx |

000q quuu |

|

|

04h |

FSR |

Indirekt címzö regiszter (adatmemória) |

xxxx xxxx |

uuuu uuuu |

||||||||

|

05h |

PORTA |

|

|

|

RA4/T0CKI |

RA3 |

RA2 |

RA1 |

RA0 |

x xxxx |

u uuuu |

|

|

06h |

PORTB |

RB7 |

RB6 |

RB5 |

RB4 |

RB3 |

RB2 |

RB1 |

RB0/INT |

xxxx xxxx |

uuuu uuuu |

|

|

07h |

Nem létezö, olvasáskor 0-t ad |

|

|

|||||||||

|

08h |

EEDATA |

EEPROM adat regiszter |

xxxx xxxx |

uuuu uuuu |

||||||||

|

09h |

EEADR |

EEPROM cím regiszter |

xxxx xxxx |

uuuu uuuu |

||||||||

|

0Ah |

PCLATH |

|

|

|

A PC felsö 5 bitjének írható puffere(1) |

|

|

|||||

|

0Bh |

INTCON |

GIE |

EEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

0000 000u |

|

|

Bank 1 |

||||||||||||

|

80h |

INDF |

Az FSR által kijelölt fájlregiszter adatát tartalmazza (fizikailag nem létezik) |

|

|

||||||||

|

81h |

OPTION_REG |

|

INTEDG |

T0CS |

T0SE |

PSA |

PS2 |

PS1 |

PS0 |

|

|

|

|

82h |

PCL |

A programszámláló (PC) alsó 8 bitje |

|

|

||||||||

|

83h |

STATUS(2) |

IRP |

RP1 |

RP0 |

|

|

Z |

DC |

C |

0001 1xxx |

000q quuu |

|

|

84h |

FSR |

Indirekt címzö regiszter (adatmemória) |

xxxx xxxx |

uuuu uuuu |

||||||||

|

85h |

TRISA |

|

|

|

PORTA irányát kijelölö regiszter |

|

|

|||||

|

86h |

TRISB |

PORTB irányát kijelölö regiszter |

|

|

||||||||

|

87h |

Nem létezö, olvasáskor 0-t ad |

|

|

|||||||||

|

88h |

EECON1 |

|

|

|

EEIF |

WRERR |

WREN |

WR |

RD |

0 x000 |

0 q000 |

|

|

89h |

EECON2 |

EEPROM vezérlö regiszter (fizikailag nem létezik) |

|

|

||||||||

|

8Ah |

PCLATH |

|

|

|

A PC felsö 5 bitjének írható puffere(1) |

|

|

|||||

|

8Bh |

INTCON |

GIE |

EEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

0000 000u |

|

Jelölések: x=ismeretlen, u=nem változik, -=nem létezö olvszva 0, q=értéke feltételektöl függ

Megjegyzések:

1: A programszámláló felsö 5 bitje közvetlenül nem hozzáférhetö (csak az alsó 8 bitet (PCL) lehet közvetlenül írni. A PCLATH regiszter szolgál a PC felsö bitjeinek ( PC<12:8>) kezelésére. Vezérlésátadó utasítás esetén a PCH-ba innen töltödik be a felsö öt bitet

A STATUS regiszter ![]() és

és ![]() bitjeire a külsö

bitjeire a külsö ![]() reset nincs hatással.

reset nincs hatással.

3: Az egyéb nem bekapcsolási reset feltételek a következök:

- külsö reset az ![]() lábon keresztül

lábon keresztül

- Watchdog Timer reset

A STATUS regiszter az ALU jelzöbitjeit,

a bankválasztó biteket, valamint a CPU állapotáról tájékoztató biteket

tartalmazza. A ![]() és

és ![]() bitek csak

olvashatóak, a többi írható is. Abban az esetben, ha valamely utasításban

célként szerepel a STATUS regiszter, akkor a Z, DC, C bitek nem írthatók, ezeket

a rendszerlogika állítja. A BCF, BSF MOVWF utasításokkal az írható bitek

tetszés szerinti értékre állíthatók. Például a CLRF STATUS utasítás törli a

felsö három bitet, egybe állítja a Z bitet, a többit pedig változatlanul

hagyja. A STATUS regiszter felépítése a következö:

bitek csak

olvashatóak, a többi írható is. Abban az esetben, ha valamely utasításban

célként szerepel a STATUS regiszter, akkor a Z, DC, C bitek nem írthatók, ezeket

a rendszerlogika állítja. A BCF, BSF MOVWF utasításokkal az írható bitek

tetszés szerinti értékre állíthatók. Például a CLRF STATUS utasítás törli a

felsö három bitet, egybe állítja a Z bitet, a többit pedig változatlanul

hagyja. A STATUS regiszter felépítése a következö:

|

R/W-0 |

R/W-0 |

R/W-0 |

R-1 |

R-1 |

R/W-x |

R/W-x |

R/W-x |

|

IRP |

RP1 |

RP0 |

|

|

Z |

DC |

C |

IRP: regiszter lapválasztó bit indirekt címzéshez (a 16F84-ben nem használatos, késöbbi fejlesztésre fenntartva)

RP1, RP0: regiszter lapválasztó bitek direkt címzéshez (a 16F84-ben csak az RP0 müködik

00 Bank 0 (00h-7Fh)

01 = Bank 1 (80h-FFh)

Mindkét bank 128 bájtból áll. Az RP1-et nullában kell tartani!

![]() : Time Out bit

: Time Out bit

1-be billen a tápfeszültség bekapcsolásakor, a CLRWDT és a SLEEP utasítás hatására

0-ba billen a watchdog timer tulcsordulására

![]() : Power Down bit

: Power Down bit

1-be billen a tápfeszültség bekapcsolásakor és a CLRWDT hatására

0-ba billen a SLEEP utasítás hatására

Z: Zero Bit

1-be billen, ha valamely aritmetikai vagy logikai müvelet eredménye nulla

DC:

Digit Carry/![]() bit (ADDLW és ADDWF utasításoknál)

bit (ADDLW és ADDWF utasításoknál)

1-be billen, ha átvitel történt a negyedik bitnél

0-ba billen, ha nem volt átvitel a negyedik bitnél

C:

Carry/![]() bit (ADDLW és ADDWF utasításoknál)

bit (ADDLW és ADDWF utasításoknál)

1-be billen, ha átvitel történt a legmagasabb súlyozású bitnél

0-ba billen, ha nem volt átvitel a legmagasabb súlyozású bitnél

Megjegyzés:

Kivonásnál a ![]() ellentétesen

müködik. A kivonást 2-es komplemensben végzi.

ellentétesen

müködik. A kivonást 2-es komplemensben végzi.

A forgatások (RRF,RLF) a carry biten keresztül történnek.

Az OPTION_REG regiszter egy írható olvasható regiszter, amely különbözö vezérlö és konfigurációs biteket tartalmaz: TMR0/WDT elöosztó, külsö INT megszakítás, TMR0, illetve a PORTB felhúzóellenállásainak beállítása.

|

R/W-1 |

R/W-1 |

R/W-1 |

R/W-1 |

R/W-1 |

R/W-1 |

R/W-1 |

R/W-1 |

|

|

|

T0CS |

T0SE |

PSA |

PS2 |

PS1 |

PS0 |

![]() : PORTB felhúzóellenállásait engedélyezö bit

: PORTB felhúzóellenállásait engedélyezö bit

1 Felhúzóellenállások tiltva

0 Felhúzóellenállások engedélyezve

INTEDG: Külsö megszakítás élválasztó bit

1 A megszakítás az RB0/INT láb felfutó élére aktív

0 A megszakítás az RB0/INT láb lefutó élére aktív

T0CS : TMR0 órajel forrását kiválasztó bit

1 Az RA4/T0CKI láb az órajel forrása

0 A belsö utasításciklus lépteti a TMR0-t

T0SE: TMR0 forrás élválasztó bit

1 A TMR0 az RA4/T0CKI lábon történt lefutó élre növekszik

0 A TMR0 az RA4/T0CKI lábon történt felfutó élre növekszik

PSA: Elöosztó hozzárendelö bit

1 Az elöosztó a WDT-hez csatlakozik

0 Az elöosztó a TMR0-hoz csatlakozik

PS2:PS0: Az osztási arányt kiválasztó bitek

|

Bitek |

TMR0 |

WDT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Megjegyzés: Ha az elöosztó a WATCHDOG TIMER-hez csatlakozik, akkor a TMR0 osztása 1:1.

Az INTCON regiszter egy írható olvasható regiszter, amely a különbözö megszakításokat engedélyezö biteket, valamint a megszakítás bekövetkezését jelzö biteket tartalmazza.

|

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-x |

|

GIE |

EEIE |

EEIE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

GIE: Általános megszakítást engedélyezö bit

1 = Megszakítások engedélyezve

0 Megszakítások tiltva

EEIE: Eeprom írás kész megszakítás engedélyezés bit

1 Eeprom írás kész megszakítás engedélyezve

0 = Eeprom írás kész megszakítás tiltva

T0IE: TMR0 tulcsordulás megszakítás engedélyezö bit

1 = TMR0 megszakítás engedélyezve

0 = TMR0 megszakítás tiltva

INTE: RB0/INT külsö megszakítás engedélyezö bit

RB0/INT külsö megszakítás engedélyezve

RB0/INT külsö megszakítás tiltva

RBIE: A PORTB felsö 4 bitjén létrejövö változás miatti megszakítás engedélyezö bit

1 = PORTB változás megszakítás engedélyezve

0 = PORTB változás megszakítás tiltva

T0IF: TMRO túlcsordulás megszakítást jelzö bit

1 TMR0 túlcsordult (szoftverböl kell törölni

0 = Nincs túlcsordulás

INTF: RB0/INT külsö megszakítást jelzö bit

1 RB0/INT külsö megszakítás érkezett (szoftverböl kell törölni

0 = Nem történt megszakítás

RBIF: A PORTB felsö 4 bitjén létrejövö változás miatti megszakítást jelzö bit

1 = V ltozás történt az RB7-RB4 lábak valamelyikén (szoftverböl kell törölni

0 = Nem történt változás RB7-RB4 lábakon

A programszámláló (PC) mutat a következö lehívandó utasításra. A PC 13 bit széles. Az alsó bájtját PCL regiszternek nevezik., amely írható és olvasható. A felsö bájtját PCH regiszternek hívják. Ez a regiszter tartalmazza a PC<12:8> bitjeit, viszont ez közvetlenül nem írható-olvasható. Minden PCH regiszterre irányuló müvelet a PCLATH regiszteren keresztül valósul meg.

A veremtár 8 szubrutinhívás vagy megszakítási esemény visszatérési címének tárolására alkalmas, azaz a verem 8 szintü és 13 bit széles. A verem hardver verem, vagyis nem része a program, illetve az adatterületnek. Ilyen módon a veremmutató nem írható és nem olvasható. A PC tartalma eltárolódik a veremben (PUSH) minden szubrutinhívó (CALL) utasítás, vagy megszakítási esemény hatására. A visszatérési utasítások (RETURN, RETLW, RETFIE) hatására a PC tartalma visszaíródik a veremböl (POP). A veremmüveleteknél (PUSH és POP) a PCLATH regiszter tartalma nem változik (természetesen a PCH az átíródik). Abban az esetben, ha a verem betelt (8 PUSH után) a verembe elöször berakott visszatérési cím felülíródik

Az INDF fizikailag nem létezö regiszter. Az INDF tulajdonképpen annak a regiszternek a tartalmát adja vissza, amelyet az FSR regiszterrel kiválasztottunk. Ez az úgynevezett indirekt címzés.

Példa az indirekt címzésre:

A 05h címen lévö regiszterfájl tartalma 10h

A 06h címen lévö regiszterfájl tartalma 0Ah

Az FSR regiszterbe betöltünk 05h-t

Olvasáskor az INDF regiszter tartalma 10h-t mutat

Eggyel megnöveljük az FSR tartalmát (06h)

Az INDF regiszter tartalma most 0Ah lesz, ha kiolvassuk

Ha az INDF regisztert, saját magát indirekt módon olvassuk (FSR 0), akkor eredményül nullát kapunk. Ha az INDF regisztert indirekt módon írjuk, akkor nem történik semmi (a jelzöbitek azonban a STATUS regiszterben beállnak).

A következö egyszerü program arra mutat példát hogyan lehet törölni a RAM területet indirekt címzéssel 20h-tól 2Fh-ig:

movlw 0x20 a mutató beállítása..

movwf FSR ;.. a RAM terület kezdetére

Next clrf INDF INDF regiszter törlése

incf FSR a mutató növelése

btfss FSR,4 kész az összes

goto Next ; nem, a következö törlése

Continue .

. igen, folytatás

A tényleges 9 bites címzés a 8 bites FSR regiszteren és az IRP (STATUS<7>) biten keresztül valósul meg, mint ahogy 6.ábrán látható.

Direkt címzés Indirekt címzés

RP1 RP0 6 (az utasítás címrésze ) 0 IRP 7 (FSR) 0

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

bank bankon belüli hely bank bankon belüli hely

választó választó

|

|

|

|

|

|

0Bh |

|

|

80h |

|

0Ch 4Fh |

|

A Bank0 tükörképe |

|

|

50h 7Fh |

|

|

FFh |

|

|

Bank0 |

Bank1 |

|

6. ábra

Megjegyzések

1: A részletes memóriatérkép az 5. ábrán látható

2: Nullában kell tartani (késöbbi felhasználásra fenntartva)

3: Nincs beépítve

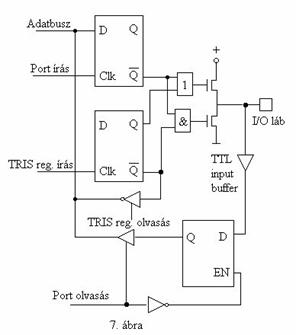

Néhány kivezetés ezen I/O portok közül multiplexált, azaz több alternatív funkció ellátására alkalmas a különbözö készülék perifériák számára. Általános esetben, ha a periféria funkció engedélyezve van, akkor a lábat nem használhatjuk általános célú I/O portként. További információ a felhasználói kézikönyvben (DS33023) található.

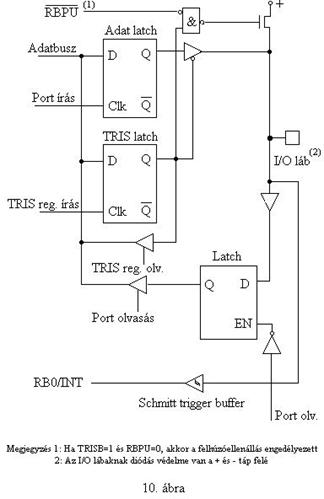

A PORTA 5 bit széles kétirányú port. Az adatirányt a TRISA regiszter bitjei határozzák meg. Amikor a TRISA bitjét 1-be állítjuk, akkor a PORTA megfelelö bitje bemenet lesz, a kimeneti drájver nagyimpedanciás (Hi-Z) lesz. Abban az esetben, ha a TRISA megfelelö bitjét 0-ba billentjük, akkor a PORTA bitje kimenet lesz.

Megjegyzés: bekapcsolási reset után a PORTA bemenetként lesz definiálva, olvasáskor pedig 0-t fog visszaadni.

Amikor olvassuk a PORTA regisztert, akkor tulajdonképpen a bemeneti D tárolóból olvassuk az adatot, amelybe a PORTA értéke íródik be.

Minden írási müvelet egy olvasás-módosítás-visszaírás müveletböl tevödik össze.

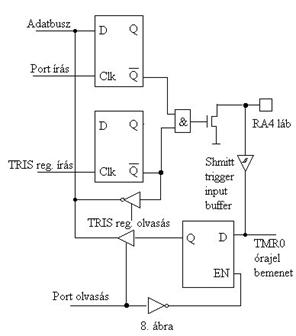

Az RA4 láb multiplexált: müködhet általános I/O portként, vagy lehet a Timer0 modul órajelforrása (T0CKI-Timer0 Clock Input). Az RA4/T0CKI láb (8. Ábra) bemenetként Schmitt-triggeres, kimenetként nyitott kollektoros (felhúzóellenállást igényel)

Mindegyik RA kivezetés TTL jelszintekkel dolgozik bemenetként, kimenetként CMOS végfokozattal rendelkezik.

Példa a PORTA beállítására:

BCF STATUS,RP0 Bank0

CLRF PORTA PORTA adattárolóinak törlése

BSF STATUS,RP0 Bank1

MOVLW B ; Adatirányok beállítása

MOVWF TRISA ; RA<3:0> bemenet, RA4 kimenet

Megjegyzés: az I/O kivezetések védödiódával rendelkeznek a plusz és a mínusz táp felé (az RA4 csak a mínusz felé).

|

Név |

Bit |

Buffer típus |

Funkció |

|

RA0 |

|

TTL |

Bemenet/kimenet |

|

RA1 |

|

TTL |

Bemenet/kimenet |

|

RA2 |

|

TTL |

Bemenet/kimenet |

|

RA3 |

|

TTL |

Bemenet/kimenet |

|

RA4/T0CKI |

|

ST |

Bemenet/kimenet vagy külsö órajelforrás a TMR0-hoz Nyitott kollektoros |

|

Cím |

Név |

Bit7 |

Bit6 |

Bit5 |

Bit4 |

Bit3 |

Bit2 |

Bit1 |

Bit0 |

Bekapcs. reset utáni érték |

Egyéb reset utáni érték |

|

|

05h |

PORTA |

|

|

|

RA4/ T0CKI |

RA3 |

RA2 |

RA1 |

RA0 |

---x xxxx |

---u uuuu |

|

|

85h |

TRISA |

|

|

|

TRISA4 |

TRISA3 |

TRISA2 |

TRISA1 |

TRISA0 |

|

|

|

Jelölések: x=ismeretlen, u=nem változik, -=nem létezö olvasva 0, q=értéke feltételektöl függ

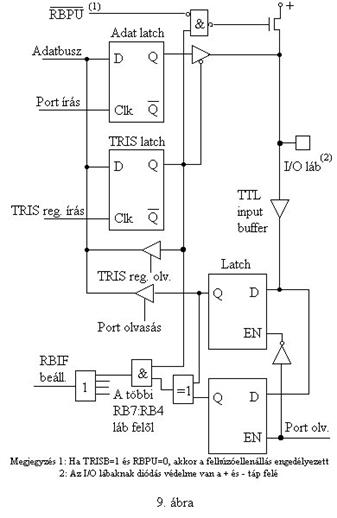

A PORTB 8 bit széles kétirányú port. Az adatirányt a TRISB regiszter határozza meg. Amikor a TRISB bitjét 1-be állítjuk, akkor a PORTB megfelelö bitje bemenet lesz, a kimeneti drájver nagyimpedanciás (Hi-Z) lesz. Abban az esetben, ha a TRISB megfelelö bitjét 0-ba billentjük, akkor a PORTB bitje kimenet lesz.

Példa a PORTB beállítására:

BCF STATUS,RP0 Bank0

CLRF PORTB PORTA adattárolóinak törlése

BSF STATUS,RP0 Bank1

MOVLW B ; Adatirányok beállítása

MOVWF TRISB ; RB<3:0> bemenet,

; RB<5:4> kimenet

; RB<7:6> bemenet

Mindegyik PORTB

kivezetés rendelkezik belsö felhúzóellenállással. A

felhúzóellenállások bekapcsolása az ![]() (OPTION_REG<7>)

bit 0-ba állításával történik, amely minden bithez hozzárendeli a

felhúzóellenállást! A felhúzóellenállás automatikusan kikapcsolódik, ha a lábat kimenetként

definiáljuk. Bekapcsolási reset után a felhúzóellenállások tiltva vannak.

(OPTION_REG<7>)

bit 0-ba állításával történik, amely minden bithez hozzárendeli a

felhúzóellenállást! A felhúzóellenállás automatikusan kikapcsolódik, ha a lábat kimenetként

definiáljuk. Bekapcsolási reset után a felhúzóellenállások tiltva vannak.

Négy PORTB láb (RB7:RB4) rendelkezik megszakítási lehetöséggel, ha változás lép fel ezeken a lábakon. Ez a lehetöség csak akkor müködik, ha bemeneteknek programozzuk ezeket a lábakat. Ebben az esetben úgy müködik a megszakítás, hogy a hardver összehasonlítja a régi eltárolt PORTB bitkombinációt a jelenleg mintavételezettel, s ha változást talál bármelyik RB7:RB4 bitben, egy megszakítást generál, vagyis az RBIF (INTCON<0>) jelzöbit értéke logikai 1 lesz. Ezen megszakítás hatására a CPU felébred a SLEEP módból. A megszakítást a felhasználónak kell nyugtáznia a kiszolgáló rutinból a következö módok valamelyikével:

Minden írási vagy olvasási müvelet amely a PORTB-re irányul törli a hibafeltételt

Az RBIF jelzöbit törlése

A PORTB jól felhasználható például egy 3x4-es mátrix tasztatúra lekezelésére, felhasználva a beépített felhúzóellenállások, valamint a felsö négy bit változása miatt bekövetkezö megszakítás adta lehetöséget. Ezzel a módszerrel megspórolhatjuk a billentyüzet folyamatos lekérdezését (polling).

|

Név |

Bit |

Buffer típus |

Funkció |

|

RB0/INT |

|

TTL/ST(1) |

Bemenet/kimenet vagy külsö megszakítás bemenet szoftverböl bekapcsolható belsö felhúzóellenállással |

|

RB1 |

|

TTL |

Bemenet/kimenet szoftverböl bekapcsolható belsö felhúzóellenállással |

|

RB2 |

|

TTL |

Bemenet/kimenet szoftverböl bekapcsolható belsö felhúzóellenállással |

|

RB3 |

|

TTL |

Bemenet/kimenet szoftverböl bekapcsolható belsö felhúzóellenállással |

|

RB4 |

|

ST |

Bemenet/kimenet (változás hatására megszakítás) szoftverböl bekapcsolható belsö felhúzóellenállással |

|

RB5 |

|

TTL |

Bemenet/kimenet (változás hatására megszakítás) szoftverböl bekapcsolható belsö felhúzóellenállással |

|

RB6 |

|

TTL/ST(2) |

Bemenet/kimenet (változás hatására megszakítás) szoftverböl bekapcsolható belsö felhúzóellenállással Programozásnál órajelbemenet |

|

RB7 |

|

TTL/ST(2) |

Bemenet/kimenet (változás hatására megszakítás) szoftverböl bekapcsolható belsö felhúzóellenállással Programozásnál adatvonal |

|

Cím |

Név |

Bit7 |

Bit6 |

Bit5 |

Bit4 |

Bit3 |

Bit2 |

Bit1 |

Bit0 |

Bekapcs. reset utáni érték |

Egyéb reset utáni érték |

|

05h |

PORTA |

RB7 |

RB6 |

RB5 |

RB4 |

RB3 |

RB2 |

RB1 |

RB0 |

xxxx xxxx |

uuuu uuuu |

|

85h |

TRISA |

TRISB7 |

TRISB6 |

TRISB5 |

TRISB4 |

TRISB3 |

TRISB2 |

TRISB1 |

TRISB0 |

|

|

Jelölések: x=ismeretlen, u=nem változik, -=nem létezö olvasva 0, q=értéke feltételektöl függ

I/O programozási szempontok

Kétirányú I/O portok

Minden írási müvelet egy olvasás-módosítás-visszaírás müveletböl tevödik össze. Például a BSF és BCF utasításnál a CPU beolvassa a regisztert, végrehajtja a bit müveletet, majd viszzaírja az eredményt a regiszterbe. Óvatosan kell eljárnunk azonban akkor, ha egyazon port bitjeit bemenetnek és kimenetnek is definiáljuk. Például a BSF PORTB,5 utasítás beolvassa a PORTB mind a nyolc bitjét, 1-be állítja az 5-ös bitet, majd visszaírja az eredményt. Tételezzük fel, hogy egy bitet kétirányú I/O portként használunk, s jelenleg bemenetként definiáltuk. Ilyenkor olvasás esetén a CPU beolvassa a bitet és a bithez tartozó adat latch-et felülírja. Amíg bemenetként használjuk ezt a lábat nincs is semmilyen baj, azonban, ha késöbb kimenetként definiáljuk az adatregiszter tartalma ismeretlen lesz.

Olvasáskor a port tényleges állapotát olvassuk be, íráskor azonban nem közvetlenül a portot, hanem az adattárolókat írjuk.

A portokat kimenetként használva azokat más készülék kimeneteivel összekötve a chip tönkremenetelét idézzük elö.

Példa az olvasás-módosítás-visszaírás típusú utasításra a PORTB-n

; Kezdeti port be llítások: PORTB<7:4> bemenet

; PORTB<3:0> kimenet

; PORTB<7:6> belsö felhúzóellenállása bekapcsolva

Nincs más áramkörhöz csatlakoztatva

PORT latch PORT l b

; ----------- ---------

BCF PORTB,7 ; 01pp pppp 11pp pppp

BCF PORTB ; 10pp pppp 11pp pppp

BSF STATUS,RP0

BCF TRISB,7 ; 10pp pppp 11pp pppp

BCF TRISB,6 ; 10pp pppp 10pp pppp

; amikor TRISB,6-ot 0-ba állítjuk a PORTB,6-os láb logikai

1 lesz, mivel a latch-be elözöleg 1 íródott (lásd elsö sor)

Egymást követö I/O müveletek ugyanazon porton

Tételezzük fel a következöt: ugyanazon portra kiírunk egy adatot, majd közvetlenül utána beolvassuk a port állapotát. Elvileg nem követtünk el hibát, azonban, ha nem várjuk ki azt az idöt, amíg a port lábán a feszültség stabilizálódik, akkor elöfordulhat, hogy a kivezetés elözö állapotát olvassuk be. Ez a hiba kiküszöbölhetö úgy, hogy az írás és olvasás közé beszúrunk egy NOP utasítást, vagy egy olyan müveletet, amely nem erre a portra irányul.

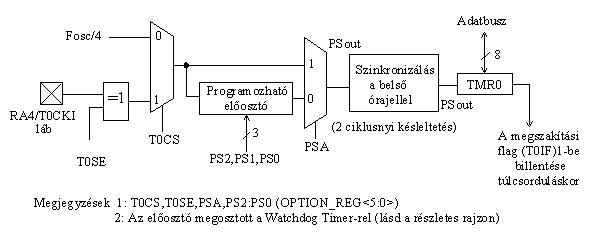

A TMR0 idözítö/számláló föbb jellemzöi:

8 bites idözítö/számláló

Írható és olvasható

Belsö vagy külsö órajel forrás

Külsö órajelnél élv kiválasztási lehetöség (lefutó vagy felfutó)

8 bites szoftverböl programozható elöosztó

Megszakítás túlcsordulás esetén (ha FFh-ból 00h-ba vált a TMR0 regiszter

A TMR0 modul egyszerüsített blokkvázlata a 11. ábrán látható. További információ a felhasználói kézikönyvben (DS33023) található.

11. ábra

A Timer0 müködhet számlálóként vagy idözítöként.

Idözítöként akkor müködik, ha T0CS bitet (OPTION REG<5>) 0-ba állítjuk, számlálóként pedig akkor, ha 1-be billentjük. Idözítö módban minden utasításciklus eggyel növeli a TMR0 regiszter értékét (feltéve, hogy nincs elöosztás). A felhasználó felül tudja írni a TMR0 regisztert (adott értékkel feltöltheti) , ilyenkor az elöbb említett növelés letiltódik a következö két utasításciklus erejéig.

Számláló módban a TMR0 regiszter értéke növekszik minden felfutó vagy lefutó él hatására, amely az RA4/T0CKI lábon történik. A felfutó vagy lefutó él kiválasztása a T0SE bittel (OPTION REG<4>) történik. Nullába állítva ezt a bitet felfutó élre történik, 1-be állítva pedig lefutó élre történik a növelés. Külsö órajel forrás használata estén a következö megszorításokkal kell élnünk: biztosítani kel, hogy a külsö órajel szinkronizálva legyen a belsö órajel fázisához, ami miatt késedelmet szenved a TMR0 aktuális növelése. További információ a külsö órajelröl a felhasználói kézikönyvben (DS33023) található.

A 8 bites számláló regiszter lehet a Timer0 modul elöosztója, vagy a Watchdog Timer utóosztója, mint ahogy a 12. Ábrán látható. Mivel csak egy regiszterünk van, amely megosztott a Timer0 modul és a Watchdog Timer között, ezért, ha az elöosztót a Timer0 modulhoz rendeljük, akkor a Watchdog Timer-nek nincs osztója, s ez ugyanígy fordítva is igaz. Az elöosztó nem írható és nem is olvasható. A PSA bit (OPTION_REG<3>) hat rozza meg, hogy az elöosztó hová kapcsolódik. Ha a PSA bit értéke 0, akkor az osztó a Timer0 modulhoz, ha 1, akkor a Watchdog Timer-hez kapcsolódik. Az osztás mértékét a PS2:PS0 bitek határozzák meg. Ha az osztó a Timer0 modulhoz kapcsolódik, akkor az értékek 1:2, 1:4..1:256 között alakulnak, ha a Watchdog Timer-hez kapcsolódik, akkor pedig 1:1, 1:2..1:128 közötti értékeket vehet fel. Ha a Timer0 modulhoz van rendelve az osztó, akkor minden utasítás írja a TMR0 regisztert, ha Watchdog Timer-hez van rendelve, akkor a CLRWDT utasítás törli a regisztert.

Timer0 megszakítás

A Timer0 megszakítás akkor keletkezik, amikor a TMR0 regiszter túlcsordul, azaz FFh-ból 00h-ba vált. Ez a túlcsordulás beállítja a T0IF bitet (INTCON<2>). Ez a megszakítás maszkolva van a T0IE bittel, azaz csak akkor él, ha ez bit logikai 1 (a GIE bit minden megszakítást letilt, tehát ennek is 1-nek kell lennie). A T0IF bitet szoftverböl kell a kiszolgáló rutinban törölni (ez nagyon fontos kritérium). A TMR0 megszakítás nem ébreszti fel alvó állapotból a processzort, SLEEP állapotban a TMR0 nem müködik!

EEPROM adatmemória

Az EEPROM adatmemória

|

Mnemonik Operandus |

Leírás |

Ciklus |

14 bites kód |

Állított jelzöbitek |

Megjegyzés |

|

MSB LSB |

|||||

|

Bájt orientált fájlregiszter müveletek |

|||||

|

ADDWF f,d |

W és f összeadása |

|

00 0111 dfff ffff |

C,DC,Z |

|

|

ANDWF f,d |

W és f ÉS kapcsolata |

|

00 0101 dfff ffff |

Z |

|

|

CLRF f |

f törlése |

|

00 0001 1fff ffff |

Z |

|

|

CLRW |

W törlése |

|

00 0001 0xxx xxxx |

Z |

|

|

COMF f,d |

f komplementálása |

|

00 1001 dfff ffff |

Z |

|

|

DECF f,d |

f csökkentése |

|

00 0011 dfff ffff |

Z |

|

|

DECFSZ f,d |

f csökkentése és ugrás, ha 0 |

|

00 1011 dfff ffff |

|

|

|

INCF f,d |

f növelése |

|

00 1010 dfff ffff |

Z |

|

|

INCFSZ f,d |

f növelése és ugrás, ha 0 |

|

00 1111 dfff ffff |

|

|

|

IORWF |

f és W VAGY kapcsolata |

|

00 0100 dfff ffff |

Z |

|

|

MOVF f,d |

f mozgatása |

|

00 1000 dfff ffff |

Z |

|

|

MOVWF f |

W mozgatása f-be |

|

00 0000 1fff ffff |

|

|

|

NOP |

nincs müvelet |

|

00 0000 0xx0 0000 |

|

|

|

RLF f,d |

forgatás balra az átvitelbiten keresztül |

|

00 1101 dfff ffff |

C |

|

|

RRF f,d |

forgatás jobbra az átvitelbiten keresztül |

|

00 1100 dfff ffff |

C |

|

|

SUBWF f,d |

W kivonása az f-böl |

|

00 0010 dfff ffff |

C,DC,Z |

|

|

SWAPF f,d |

az f alsó és felsö 4 bitjének cseréje |

|

00 1110 dfff ffff |

|

|

|

XORWF f,d |

W és f kizáró-vagy kapcsolata |

|

00 0110 dfff ffff |

Z |

|

|

Bit orientált fájlregiszter müveletek |

|||||

|

BCF f,b |

az f adott bitjének törlése |

|

01 00bb bfff ffff |

|

|

|

BSF f,b |

az f adott bitjének 1-be billentése |

|

01 01bb bfff ffff |

|

|

|

BTFSC f,b |

a bit tesztelése és ugrás, ha 0 |

|

01 10bb bfff ffff |

|

|

|

BTFSS f,b |

a bit tesztelése és ugrás, ha 1 |

|

01 11bb bfff ffff |

|

|

|

Konstans és vezérlésátadó müveletek |

|||||

|

ADDLW k |

konstans hozzáadása a W-hez |

|

11 11x kkkk kkkk |

C,DC,Z |

|

|

ANDLW k |

W és egy konstans ÉS kapcsolata |

|

11 1001 kkkk kkkk |

Z |

|

|

CALL k |

szubrutin hívás |

|

10 0kkk kkkk kkkk |

|

|

|

CLRWDT |

Watchdog Timer törlése |

|

|

|

|

|

GOTO k |

ugrás címkére |

|

10 1kkk kkkk kkkk |

|

|

|

IORLW k |

W és egy konstans VAGY kapcsolata |

|

11 1000 kkkk kkkk |

Z |

|

|

MOVLW k |

konstans mozgatása a W-be |

|

11 00xx kkkk kkkk |

|

|

|

RETFIE |

visszatérés a megszakításból |

|

|

|

|

|

RETLW k |

visszatérés szubrutinból egy konstanssal |

|

11 01xx kkkk kkkk |

|

|

|

RETURN |

visszatérés szubrutinból |

|

|

|

|

|

SLEEP |

váltás alvó módba |

|

|

|

|

|

SUBLW k |

W kivonása egy konstansból |

|

11 110x kkkk kkkk |

C,DC,Z |

|

|

XORLW k |

W és egy konstans kizáró-vagy kapcsolata |

|

|

|

|

Megjegyzések:

Amikor a d helyén 1 (vagy f) áll, akkor az eredmény saját magába íródik vissza (fájlregiszter), ha pedig a d helyén 0 (w) áll, akkor a w regiszterbe íródik be.

Abban az esetben, ha a müvelet a TMR0 regiszterre vonatkozik (d 1, vagy d=f), és az elöosztó a TMR0-hoz van rendelve, akkor az elöosztó törlödik.

Amikor a programszámláló (PC) változik az utasítás két ciklus hosszú lesz. A második ciklusban a NOP utasítás kerül végrehajtásra.

Találat: 2746