| kategória | ||||||||||

|

| ||||||||||

|

| ||

|

||||||||||

Dekódolás (alkalmazott eljárások áttekintése, párhuzamos hagyományos dekódolók, elödekódolás, a trace cache használata, példák)

Dekódolási lehetöségek:

Mivel a szuperskalár processzorokat jellemzöen több utasítás kibocsátása jellemzi, ezért a párhuzamos dekódolás itt egy komplexebb feladat, mint az egyszerü skalár processzorokban. Magasabb kibocsátási ráták esetén túlzottan megnöhet a dekódolási ciklus hossza vagy ez a dekódolás továbbfejlesztése nélkül oda vezethet, hogy egy dekódolási ciklus helyett a processzornak két vagy több ciklusra lesz szüksége.

Skalár processzoroknak ciklusonként csak egyetlen utasítást kell dekódolnia, ezen felül ellenöriznie kell, hogy a kibocsátandó utasítás függ-e a végrehajtás alatt állóktól és így kibocsátható-e. A szuperskalár processzor ennél összetettebb. Minden ciklusban több, általában négy utasítást kell egy idöben dekódolni, ezen felül meg kell vizsgálnia, hogy a kibocsátás alatt álló utasítások függenek-e a jelenleg végrehajtás alatt állóktól, illetve, hogy van-e függöség a következö ciklusban kibocsátásra váró utasítások között. Mivel a szuperskalár processzorban több végrehajtó egység is van, ezért ezek a függöség vizsgálatok sokkal több összehasonlítást jelentenek, mint a skalárokban. Összességében tehát a kibocsátási ráta növelésével nö a dekódolás komplexitása. Ez nyilván a teljesítményben mutatkozik meg.

Hagyományos:

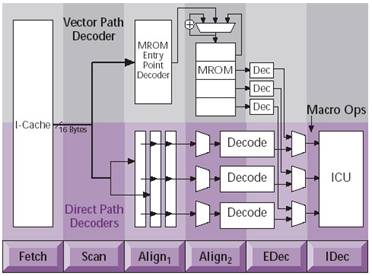

A hagyományos dekódolás egy egyszerü párhuzamos dekódolás. Ezt az elsö generációs RISC-ek és a késöbbi CISC processzorok használják. A második generációs CISC processzorokban többnyire egy RISC magot valósítottak meg. Ilyenkor a dekódolás során a CPU elött egy CISC-RISC konverziót végez, melynek során egy CISC utasítást RISC utasítások sorára bontja. Pentium Pro-ban 16 bájt töltödik fel a dekóderekben. Ezekböl az 1. elfogad bármilyen CISC utasítást, ami maximum három RISC utasítással dekódolható. A második-harmadik, egyszerü dekóder viszont csak egy RISC utasítással dekódolható CISC-eket fogad el (pl load vagy egy regiszter operáció). Akkor van tehát hármas feltöltés, ha az utasítás legfeljebb három RISC utasítással dekódolható és rögtön utána két olyan utasítás jön, melyek egy-egy RISC utasításokkal dekódolhatóak. Ez nagyon ritkán fordul elö. A komplexebb utasításokhoz egy mikor-utasítás ROM tartozik, mely ciklusonként három utasítást bocsát ki. Ezek felváltva dolgoznak, vagyis vagy a három alapdekóder müködik vagy a mikro-utasítás ROM. Az AMD K6 processzorának egy nagyon hasonló dekódere van. Ebben a három alapdekóder mellett egy ún. vektor dekóderrel találkozunk, mely gyakorlatilag megegyezik a Pentium Pro mikro-utasítás ROM-jával. Az Athlon (K7) abban különbözik az elözöektöl, hogy a három alapdekóder teljesen egyenrangú:

A dekódolás után a kibocsátáshoz egy visszaalakítást végez. Ennek során összeláncolják az egy CISC utasításhoz tartozó RISC utasításokat, és csak együtt engedik öket kibocsátani (ROB).

Elödekódolás

A növekvö kibocsátás hatásának csökkentésére a szuperskalár processzorokban bevezették az elödekódolás folyamatát. Az utasítás cache feltöltésekor az L2 cache (vagy ennek híján a memória) és az utasítás cache közé egy hardware egység kerül, mely utasításokhoz RISC-eknél 4-7, CISC-eknél 2-5 bitet füz hozzá. Egyszerre 128 bit jön le az L2 cache-böl. Ez tehát még a feltöltéskor történik, így nem jelent idökritikus müveletet. Az elödekódolás megjelenése jellemzöen 1995-re tehetö, vagyis a második generációs rendszereknél, mivel itt nöt meg a kibocsátási ráta, itt vált szükségessé ennek a technikának a bevezetése. Ez nem sokkal az elsö generációs rendszerek megjelenése után jött, 2-3 évvel ezek bevezetése után. Rohamos elterjedésük elsösorban annak köszönhetö, hogy az ilyen technikákkal kapcsolatos tervek hamar kikerülnek a titok köréböl, így többnyire egyszerre tudnak kijönni a gyártók az új megoldásokkal. A többlet bitekre jellemzö, hogy elsösorban CISC rendszereknél terjedtek el és az idö elörehaladtával csökkentek (pl K8-ban már csak 2 bit).

Trace cache:

Jellemzöen az Intel P4-ben, vagyis egy harmadik generációs CISC rendszerben jelent meg. Lényege az a felismerés, hogy az utasítások kb. 80%-át a ciklusok végrehajtása jelenti, így azonos utasítások folyamatos lehívásával és dekódolásával felesleges müveleteket végzünk. Ötlet: a dekódolt utasításokat tárolni kell, s a ciklusok végrehajtását a tároltak lehívásával gyorsítani.

Találat: 685