|

|

||

|

||||||||||||||||||

Logikai tervezés

Elõadásvázlat

4. elõadás,

Egyszerû PLD eszközök (folytatás)

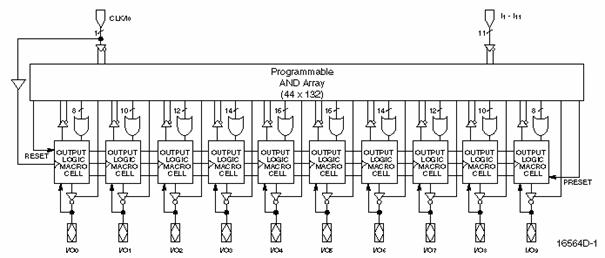

A 22V10 típus

A legszélesebb körben elterjedt eszköz, gyakorlatilag ipari szabvány

Tulajdonságok: változó számú p-term, kimenetenként 8-10-12-14-16-16-14-12-10-8

polaritás váltás a kimeneten (HIBA!)

közvetlen CLK, lehet bemenet is, nincs dedikált OE láb

regiszterekre közös aszinkron p-term RESET és szinkron PRESET

A 22V10 kimeneti makro cellája

Egyszerû tiszta struktúra, átlátható mûködési módok

Visszacsatolás regiszteres kimenetnél a PAL-okhoz hasonlóan a regiszter /Q

kimenetérõl, itt viszont a polaritás váltás a kimeneten történik

Következmények:

1. A kombinációs kimeneti vcs. követi a polaritás váltást

A regiszteres kimeneti vcs. nem követi a polaritás váltást

2. Az AR és SP termek hatása a belsõ regiszterekre vonatkozik, a polaritástól függõen

a kimenet ettõl eltérõen is beállhat

Érdekesebb továbbfejlesztések:

Intel 85C22V10 programozható órajel polaritás

NSC SCAN22V10 28PLCC foglalat, 4 extra láb beépített JTAG teszt interfész

Egyéb, részletesen nem tárgyalt érdekesebb egyszerû PLD típusok

Atmel ATV750 dupla regiszter a kimeneti makro cellában, többszörös vcs.

(belsõ, eltemetett logika!!!)

Intel 5AC312 bemeneti makro cellák, két órajel bemenet

p-term megosztás: átlagos komplexitás nem nõ,

extra igények kezelhetõk

TURBO/LOW POWER üzemmód

Az utolsó jelváltás után néhány 100 ns múlva LP üzemmódba kapcsol, a kimeneti jelszintek megtartása mellett.

Az elsõ bemeneti változásra kb. 20ns alatt feléled és további tPD

kapcsolási idõ múlva válaszol a kimeneten

Altera EP610

Egyszerû PLD a komplex PLD-k szinte összes tulajdonságával

- kis számú speciális bemeneti láb, nagyszámú., azonos I/O

- lábhoz kötött, azonos makro cellák, egyszerû, reguláris felépítés

- globális belsõ huzalozás, minden jel minden makro cella számára elérhetõ

Blokkvázlat

A makro cella felépítése

Jellemzõk: - a kimeneti regiszter típusa lehet D, T, JK, SR

- OE/CLK programozás nem teljesen független

(Mode0: OE pterm, CLK globális, szinkron,

Mode1: OE engedélyezett, CLK p-term, aszinkron)

Alkalmazási szempontok az órajel kiválasztásához

Szinkron, globális CLK:

minden regiszter azonos órajelet kap

az órajel belsõ késleltetése kicsi,

hosszú elõkészítési idõ, rövid tartási idõ

Aszinkron CLK: az órajel belsõ késleltetése azonos az adatokkal

rövid elõkészítési idõ, normális tartási idõ (normális viselkedés), viszont hosszú

a tCQ kimeneti kapcsolási válaszidõ

Tervezés, implementáció:

1. Tervezési elképzelések:

Szükséges eszköz komplexitás becslése, (lábszám, kimenetek, sebesség, fogyasztás)

2. Terv elõkészítés:

Általában valamilyen leíró nyelv vagy kapcsolási rajz szerkesztõ használatával

HDL Hardware Description Language pl. ABEL, PALASM, AHDL, CUPL

Logikai feladat megfogalmazása: egyenletek, igazságtábla, állapot átmeneti tábla.

3. Terv feldolgozása

Szintaktikai elemzés,

Egyenletek rendezése, SOP formátum generálása,

Fordítás, állapotleírások, igazságtáblázatok kifejtése,

Minimalizálás, optimalizáció,

4. Szimuláció

Tesztkörnyezet beállítása, vektorok generálása

Logikai, funkcionális szimuláció (csak a logikai egyenletek ellenõrizhetõk!)

5. Optimalizálás, leképezés

Eszközfüggõ tulajdonságok figyelembevétele és kihasználása

Ponált-negált függvények

Együttes/független minimalizálás

6. Konfigurációs, programozói file generálása (JEDEC file)

Eszköz specifikus JEDEC file generálása

7. Szimuláció a JEDEC file alapján

Eszközmodell használata, nem az egyenleteket szimuláljuk!!

Megjegyzés: A JEDEC leírás és az eszközmodell lapján lehetséges a logikai funkciót

megvalósító ABEL file generálása (természetesen nem az eredeti forrás, csak

egy azonos funkcionalitást megvalósító verzió)

8. Programozás

A programozó algoritmusok GYÁRTÓ és VERZIÓ!!! specifikusak, azonos típus egyes

változatai egyedi programozói algoritmusokat igényelhetnek

Találat: 2180